# Analysis and Design of Low Power High Speed Dynamic Latch Comparator using CMOS Process

A.Sathishkumar, S.Saravanan

**Abstract**— This paper presents the need for ultra low-power, area efficient and high speed analog-to-digital converters is pushing toward the use of dynamic regenerative comparators to maximize speed and power efficiency. In this paper, an analysis on the delay of the dynamic comparators will be presented and analytical expressions are derived. From the analytical expressions, designers can obtain an intuition about the main contributors to the comparator delay and fully explore the tradeoffs in dynamic comparator design. Based on the presented analysis, a new dynamic comparator is proposed, where the circuit of a conventional double tail comparator is modified for low-power and fast operation even in small supply voltages. Without complicating the design and by adding few transistors, the positive feedback during the regeneration is strengthened, which results in remarkably reduced delay time. Post-layout simulation results in a 0.18-µm CMOS technology confirm the analysis results. It is shown that in the proposed dynamic comparator both the power consumption and delay time are significantly reduced. The maximum clock frequency of the proposed comparator can be increased to 2.5 V and 1.1 GHz at supply voltages of 1.2 and 0.6 V, while consuming 1.4 mW and 153 µW, respectively.

Index Terms— Double tail Comparator, high speed analog-to-digital converters, dynamic regenerative comparators, conventional double tail comparator, CMOS, intuition, Post-layout simulation.

#### I. INTRODUCTION 1.1 OVERVIEW

Comparator is one of the fundamental building blocks in most analog to-digital converters (ADCs). Many high speed ADCs such as flash ADCs, require high-speed, low power comparators. High-speed comparators in Ultra Deep Sub Micrometer (UDSM) CMOS technologies suffer from low supply voltages especially when considering the fact that threshold voltages of the devices have not been scaled at the same pace as the supply voltages of the modern CMOS processes. Hence, designing high-speed comparators is more challenging when the supply voltage is smaller. In other words, in a given technology, to achieve high speed, larger transistors are required to compensate the reduction of supply Voltage, which also means that more die area and power is needed. Besides, lowvoltage operation results in limited common-mode input range[8],which is important in many high-speed ADC architectures, such as flash ADCs.

# 1.2 A YIELD-OPTIMIZED LATCH-TYPE SRAM SENSE AMPLIFIER

A yield analysis of a latch-type voltage sense amplifier with a high-impedance differential input stage is presented. It quantifies the impact of supply voltage, input DC level, transistor sizing and temperature on the input offset voltage. The input dc level turns out to be most significant. Also an analytical expression for the sensing delay is derived. Experimental results in 130nm CMOS confirm that the yield can be significantly improved by lowering the input dc voltage to about 70% of the supply voltage[1]. Thereby, the offset standard deviation decreases from 19mV to 8.5mV without effecting the delay which is measured to be 119ps at 1.5V supply point (V(SO) = V(SON)). In the presence of mismatch and noise a wrong output signal can develop for small input voltage differences.

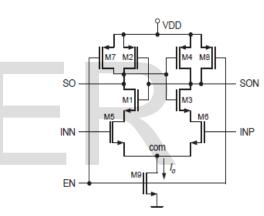

This paper investigates the design issues for this type of sense amplifier to ensure a fast and correct decision even for small input signals[10]. The transient behavior, shown in Fig.1.1 (at a large value of VDD for better visibility), consists of three phases. The enable signal EN starts the operation by turning on M9.

Fig .1. Latch-type Voltage Sense Amplifier

So an increasing output difference develops. Now strong positive feedback enhances the output voltage difference starting from an initial value Vo as marked. The latching completes during a third phase where one n-channel transistor is cut off. Then the current flow stops and the whole sense amplifier do not dissipate static power.

#### **1.3 LOW-VOLTAGE OPERATIONAL AMPLIFIER**

One of the most important basic building blocks in analog and mixed mode circuits is the operational amplifier. In a low-voltage (LV) Opamp, the minimum supply value is imposed by the differential pair of the input stage and is equal to the threshold voltage (Vth) plus two overdrive voltages (VD<sub>sat</sub>). In typical CMOS processes, this value turns out to be around 1V. On the other hand, the main limitation of differential pairs is the reduced input common-mode range (ICMR). In order to minimize the supply requirements of the input stage, both input terminals of an Opamp must work with potentials very close to one of the supply rails.

To overcome this limitation, several schemes for discrete time (switched) operation with a single supply down to 1V and large output signal swings have been recently reported. The switched-opamp (SO) technique has been shown to be a promising low-cost solution to realize switched-capacitor (SC) circuits in standard CMOS processes. The SO eliminates critical MOS switches that set the minimum supply voltage to allow sub-1-V operation[1] of the SC circuits and, thus, does not have a reliability problem. Since then, a few modifications have been proposed to improve the performance of the SO techniques in terms of operation speed and compatibility with existing SC circuits.

#### **1.4 DYNAMIC LATCHED COMPARATOR**

The dynamic latched comparator is composed of two stages. The first stage is the interface stage which consists of all the transistors except two cross coupled inverters. The second stage is the regenerative stage that is comprised of the two cross coupled inverters, where each input is connected to the output of the other. It operates in two phases.1) Interface phase and 2) Regeneration phase. It consists of single nmos tail transistor connected to ground. When clock is low tail transistor is off and depending on Vp and Vn output reaches to VDD or Gnd. When clock is high tail transistor is on and both the outputs discharges to ground. There is reduction of both power and delay in dynamic latched comparator circuit over the double tail latched and pre-amplifier based clocked comparators.

Double tail latched comparator has less power consumption but low speed because of more transistor count and pre-amplifier based clocked comparator has high speed because of less transistor count but power consumption is more because it uses an amplification stage, it consumes static power during the amplification period However, since the pre-amplifier based clocked comparator is to work at high frequency, the energy consumption of the pre-amplifier based clocked comparator becomes comparable to the double tail latched comparator. Hence the performance of the pre-amplifier based clocked comparator is limited by the static power dissipation in the evaluation or regeneration phase.

# **1.5 CLOCKED REGENERATIVE COMPARATORS**

Clocked regenerative comparators have found wide applications in many high-speed ADCs since they can make fast decisions due to the strong positive feedback in the regenerative latch[6]. Recently, many comprehensive analyses have been presented, which investigate the performance of these comparators from different aspects, such as noise, offset and random decision errors, and kick-back noise. In this section, a comprehensive delay analysis is presented; the delay time of two common structures, i.e., conventional dynamic comparator and conventional dynamic double-tail comparator are analyzed, based on which the proposed comparator will be presented.

#### **II.EXISTING SYSTEM ANALYSIS** 2.1 SINGLE TAIL COMPARATOR

Clocked regenerative comparators have found wide applications in many high-speed ADCs since they can make fast decisions due to the strong positive feedback in the regenerative latch. The schematic diagram of the conventional dynamic comparator widely used in A/D converters, with high input impedance, rail-to-rail output swing[1], and no static power consumption.

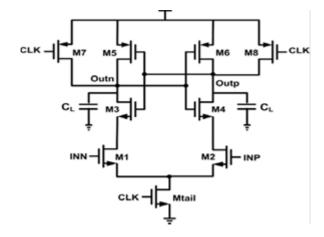

During the reset phase when CLK = 0 and Mtail is off, reset transistors (M7–M8) pull both output nodes Outn and Outp to VDD to define a start condition and to have a valid logical level during reset. In the comparison phase, when CLK = VDD, transistors M7 and M8 are off, and Mtail is on.

#### **Fig.2. Single Tail Comparator**

Output voltages (Outp, Outn), which had been pre-charged to VDD, start to discharge with different discharging rates depending on the corresponding input voltage (INN/INP). Assuming the case where VINP >VINN, Outp discharges faster than Outn, if VINP< VINN outn discharges faster than outn.

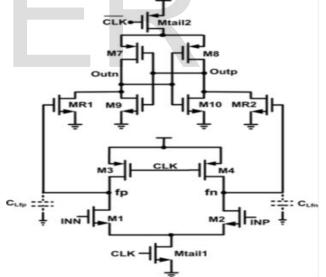

#### 2.2 CONVENTIONAL DYNAMIC COMPARATOR

The schematic diagram of the conventional dynamic comparator widely used in A/D converters[2], with high input impedance, rail-torail output swing[10], and no static power consumption[10]. The operation of the comparator is as follows. During the reset phase when CLK = 0 and Mtail is off, reset transistors (M7–M8) pull both output nodes Outn and Outp to VDD to define a start condition and to have a valid logical level during reset.

In the comparison phase, when CLK = VDD, transistors M7 and M8 are off, and Mtail is on. Output voltages (Outp, Outn), which had been pre-charged to VDD, start to discharge with different discharging rates depending on the corresponding input voltage (INN/INP). Assuming the case where VINP > VINN, Outp discharges faster than Outn, hence when Outp (discharged by transistor M2 drain current), falls down to VDD– IVthpI before Outn (discharged by transistor M1 drain current), the corresponding pMOS transistor (M5) will turn on initiating the latch regeneration caused by back-to-back inverters (M3, M5 and M4, M6). Thus, Outn pulls to VDD and Outp discharges to ground. If VINP < VINN, the circuits works vice versa.

The delay of this comparator is comprised of two time delays, t0 and tl Latch. The delay t0 represents the capacitive discharge of the load capacitance CL until the first p-channel transistor (M5/M6) turns on.

# 2.3 OFFSET VOLTAGE ANALYSIS OF DYNAMIC LATCHEDCOMPARATOR

Due to fast-speed, low-power consumption, high-input impedance and full-swing output, CMOS dynamic latched comparators are very attractive for many applications such as high-speed analog-to-digital converters (ADCs)[2], memory sense amplifiers (SAs), and data receivers. They use positive feedback mechanism with one pair of back-to-back cross coupled inverters (latch) to convert a small input-voltage difference to a full-scale digital level in a short time. However, the accuracy of such comparators is limited by the random offset voltage resulting from the device mismatches such as threshold voltage Vth, current factor  $\beta$  (= $\mu$ CoxW/L) and internal parasitic/external load capacitance mismatches.

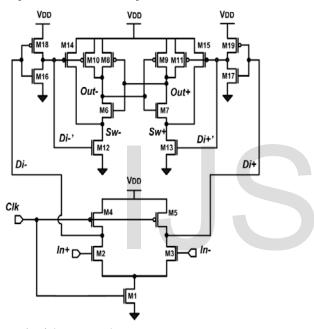

#### Fig.4.Schematic of the Proposed Comparator

The offset voltage contribution of each stage of the dynamic latched comparator[10] is analyzed and verified with the extracted ones from transient Monte- Carlo simulations. Based on the result, the dynamic latched comparator is designed and optimized. In addition to the optimum design method, a digitally controlled capacitive offset voltage compensation technique is demonstrated to further calibrate the total offset voltage using 90nm PTM technology and 1V power supply voltage[7].

#### 2.3.1 Offset Voltage Analysis Of Dynamic Comparator

The dynamic comparator shown in Figure 4 is used for our offset voltage analysis. During the pre-charge (or reset) phase (*Clk*=0V), both PMOS transistors M4 and M5 turn on and *Di* nodes' capacitances are charged to VDD, which in turn make both NMOS transistor M16 and M17 of the inverter pair on and *Di'* nodes discharge to ground. Sequentially, PMOS transistor M10, M11, M14 and M15 turn on and *Out*nodes and *Sw*nodes are charged up to VDD while both NMOS transistors M12 and M13 are off.

During evaluation (decision-making) phase (Clk=VDD), each Di node capacitance is discharged from VDD to ground in a different rate proportional to the magnitude of each input voltage. As a result, an input dependent differential voltage is formed between Di+ and Di- nodes. Once either Di+ or Di node voltage drops below VDD-|Vtp|, the inverter pairs (M18/M16 and M19/M17) invert each Di node signal into the regenerated (amplified) Di' node signals. Then the regenerated and different phased Di' node voltages are relayed to the output-latch stage by M10-M13. As the regenerated each Di' node voltage is rising from 0V to VDD with a different time interval ,M12 and M13 turn on one after another and the output latch starts regenerating the small voltage difference transmitted from Di' nodes into a full-scale digital level: Out+ node will output logic high (VDD)\ if Di+' node voltage is rising faster than Di-' node voltage and Out+ will output logic low (0V) otherwise. Once either of Out node voltages drops below VDD-|Vtp|, this positive feedback becomes stronger because either PMOS transistor M8 or M9 will turn on.

Since the dynamic comparator shown in Figure 1 can be divided into three stages, the total offset voltage (VOS, tot) can be expressed as

$$V_{OS,tot} = \sqrt{V_{OS,DiffInput}^2 + \frac{1}{G_1^2} \cdot V_{OS,Inv. Pair}^2 + \frac{1}{G_1^2 \cdot G_2^2} \cdot V_{OS,Output \, Latch}^2}$$

(1)

Where VOS\_different Input VOS\_Inv. Pair and VOS\_Ouput Latch are the offset voltages resulting from the mismatched transistor pairs in each stage, respectively[8]. G1 is the voltage gain between Di nodes and In nodes and G2 is the voltage gain between Di' nodes and Di nodes.

To optimize the comparator in terms of the minimal offset voltage, the offset voltage contributions of each stage have to be verified first. Therefore, all transistors (but the inverter pairs) are designed to have the same aspect ratio of W/L=1 $\mu$ m/0.1 $\mu$ m. In order for the inverter pair to have the proper gain and correct functionality, PMOS transistors of the inverter pair are designed three times bigger than NMOS transistors (Wp/Wn=1.5 $\mu$ m/0.5 $\mu$ m). To simulate 1-sigma offset voltages for each stage, the random mismatch[7][6] in threshold voltage Vth and current factor  $\beta$  (= $\mu$ CoxW/L) for each transistor pair are modeled as follows,

$$\sigma_{V_{th}} = \frac{A_{V_{th}}}{\sqrt{WL}}, \quad \sigma_{\beta} \models \frac{A_{\beta}}{\sqrt{WL}} \quad where W, L are in \mu m$$

(2)

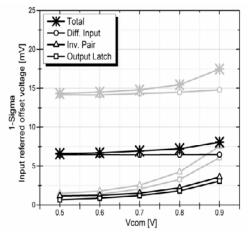

Avth and A $\beta$  are process dependent parameters and are assumed to be 4.5mV·µm and 1%·µm, respectively in this mismatch analysis. As shown in Figure 2 (in Grey), the input referred offset voltages of each stage of the comparator with respect to the different the input common mode voltages are extracted from 100 times of transient Monte-Carlo simulations (VDD=1V,fclk=3GHz). As expected, the offset voltage resulting from the mismatched transistor pairs in the regenerative output-latch stage is the smallest.

Fig.5. Offset Voltage Contributions of each stage before and after Optimization.

since it is reduced by the gain of *G1xG2* and the offset voltage from the mismatch between the inverter pair, which is reduced by the gain of *G1*, is also small comparing to the offset voltage of the differential input stage. The offset voltage of the differential input stage can be approximated.

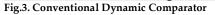

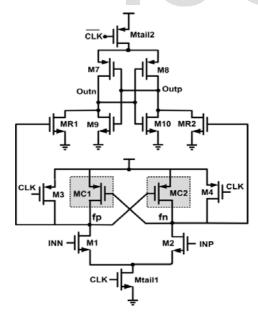

#### III. PROPOSED SYSTEM ANALYSIS 3.1 DOUBLE-TAIL DYNAMIC COMPARATOR

Due to the better performance of double-tail architecture in lowvoltage applications, the proposed comparator is designed based on the double-tail structure. The main idea of the proposed comparator is to increase *V*fn/fp in order to increase the latch regeneration speed.

For this purpose, two control transistors (MC1 and MC2) have been added to the first stage in parallel to M3/M4 transistors but in a cross-coupled manner. During compare than existing, proposed double tail comparator is efficient Power consumption and delay is efficient than existing.

Fig.6. Proposed Double Tail Dynamic Comparator

## TABLE I SUMMARY OF THE COMPARATOR PERFORMANCE

| Value     |

|-----------|

| 180-nm    |

| CMOS      |

| 1.2 V     |

| 329 µW    |

| 52) µ ((  |

| 550 ps    |

| 550 ps    |

| 69 ps/dec |

| 7.8 mV    |

| /.0 III V |

| 0.66 pJ   |

|           |

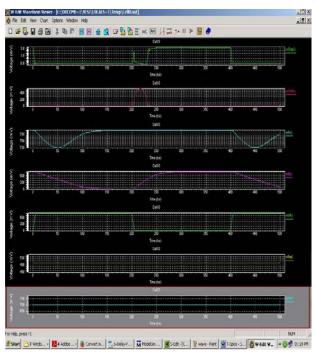

## **IV. EXPERIMENTAL RESULT**

In order to compare the proposed comparator with the conventional and double-tail dynamic comparators, all circuits have been simulated in a 0.18- $\mu$ m CMOS technology

## **INCREASED IN LEAKAGE CURRENT**

Fig.7. Simulation Result For increased in Leakage Current

The leakage current in the increased will be more due to the separation of sensing and slave latch circuit. It leads to wastage of more current.

# DECREASED IN LEAKAGE CURRENT

International Journal of Scientific & Engineering Research, Volume 5, Issue 5, May-2014 ISSN 2229-5518

Fig.8. Simulation Result For decreased Leakage Current

The leakage current in the decreased will be more due to the separation of sensing and slave latch circuit. It leads to wastage of more current.

#### TABLE II COMPARISON FOR EXISTING AND PROPOSED COMPARATOR

| Process                                | Power                | Delay                |

|----------------------------------------|----------------------|----------------------|

| Single Tail Comparator                 | 7.04*10-6 =<br>7 μW  | 6.61*10-8 =<br>66ns  |

| Conventional Double Tail<br>Comparator | 1.50*10-5 =<br>15 μW | 7.50*10-9 =<br>7.5ns |

| Proposed Double Tail<br>Comparator     | 1.29*10-5 =<br>12 μW | 7.40*10-9 =<br>7.4ns |

## **V.CONCLUSION**

In this work presented a comprehensive delay analysis for clocked dynamic comparators. Two common structures of conventional dynamic comparator and conventional double-tail dynamic comparators were analyzed. Also, based on theoretical analyses, a new dynamic comparator with low-voltage low-power capability was proposed in order to improve the performance of the comparator. Post-layout simulation results in 0.18-µm CMOS technology confirmed that the delay and energy per conversion of the proposed comparator is reduced to a great extent in comparison with the conventional dynamic comparator and double-tail comparator.

#### REFERENCES

[1] S. U. Ay, "A sub-1 volt 10-bit supply boosted SAR ADC design in standard CMOS," Int. J. Analog Integer. Circuits Signal Process., vol. 66, no. 2, pp. 213–221, Feb. 2011.

[2] A. Mesgarani, M. N. Alam, F. Z. Nelson, and S. U. Ay, "Supply boosting technique for designing very low-voltage mixed-signal circuits in standard CMOS," in Proc. IEEE Int. Midwest Symp. Circuits Syst.Dig. Tech. Papers, Aug. 2010, pp. 893–896.

[3] P. M. Figueiredo and J. C. Vital, "Kickback noise reduction technique for CMOS latched comapartors," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 53, no. 7, pp. 541–545, Jul. 2006.

[4] B. Goll and H. Zimmermann, "A comparator with reduced delay time in 65-nm CMOS for supply voltages down to 0.65," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 56, no. 11, pp. 810–814, Nov. 2009.

[5] B. Goll and H. Zimmermann, "A 0.12 μm CMOS comparator requiring 0.5V at 600MHz and 1.5V at 6 GHz," in Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers, Feb. 2007, pp. 316–317.

[6] Y. Okaniwa, H. Tamura, M. Kibune, D. Yamazaki, T.-S. Cheung, J. Ogawa, N. Tzartzanis, W. W. Walker, and T. Kuroda, "A 40Gb/s CMOS clocked comparator with bandwidth modulation technique,"IEEE J. Solid-State Circuits, vol. 40, no. 8, pp. 1680–1687, Aug. 2005.

[7] M. Maymandi-Nejad and M. Sachdev, "1-bit quantiser with rail to rail input range for sub-1V \_\_ modulators," IEEE Electron. Lett., vol. 39, no. 12, pp. 894–895, Jan. 2003

[8] B. J. Blalock, "Body-driving as a Low Voltage Analog Design Technique for CMOS technology," in *Proc. IEEE Southwest Symp. Mixed-Signal Design*, Feb. 2000, pp. 113–118.

[9] B. Goll and H. Zimmermann, "A 65nm CMOS comparator with modified latch to achieve 7GHz/1.3mW at 1.2V and 700MHz/47 $\mu$ W at 0.6V," in *Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2009,pp. 328–329.

[10] D. Shinkel, E. Mensink, E. Klumperink, E. van Tuijl, and B. Nauta, "A double-tail latch-type voltage sense amplifier with 18ps Setup+Hold time," in *Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, Feb. 2007, pp. 314–315.

# IJSER